国产精品美女一区二区视频

你的位置:国产精品美女一区二区视频 > 企业文化 >

本文由半导体产业纵横(ID:ICVIEWS)编译自semiengineering

多芯片封装凭什么成香饽饽。

跟着芯片想象变得越来越大、越来越复杂,尤其是在东谈主工智能和高性能谋划使命负载方面,将统共功能集成到单个平面芯片上通常是不切本色的。然而,何时选定多芯片封装并非老是易事。

多芯片有缱绻具有一些已被充分阐发的上风。它允许想象东谈主员将功能分拨到不同的芯片上,从而提高良率。此外,它还不错通过使用较旧、资本更低的工艺节点来制造部分组件,从而裁汰资本并提高可靠性。跟着范例的普及和器用的纠正,这些上风的终了变得愈加容易。另外,跟着性能需求的不断提高以及先进工艺节点初度芯片见服从的下落,企业更有能源选定多芯片措置有缱绻,以保持竞争力并更灵验地管制功耗、资本和可靠性。

从想象到制造经由的两头,两股主要力量正在推动多芯片封装的发展。“最初是解耦,”西门子EDA中央工程措置有缱绻总监Pratyush Kamal示意,“芯片尺寸越来越大,尤其是在非常先进的节点上,它们还是接近光罩的尺寸,而晶圆制造工艺又受到光罩尺寸的限度,这变成了一个问题。咱们正在筹商Cerebras公司怎样利用一项新时刻,将想象积贮到光罩界限以外。刻下,咱们利用晶圆级封装时刻来终了相似的缱绻,举例使用后头RDL等。关联词,对于单片想象而言,界限仍然是光罩。推动先进封装应用的第二个成分是系统集成。这里指的是镶嵌式电压周折器。咱们将更多组件集成到封装内。从根蒂上讲,淌若咱们削弱电子想象的占大地积,就能爽脆功耗,进步性能。这两个成分正在推动先进封装的普及。”

然而,哪种多芯片有缱绻才是最好采用,这是一个难以回复的问题。“你不错选定范例封装,将两个芯片并列扬弃,通过UCIe或其他芯片间积贮形势积贮,”Cadence家具营销总监Mayank Bhatnagar讲解谈。“你不错选定中间带有硅中介层的先进封装,这诚然资本更高。你甚而不错选定双芯片堆叠,或者垂直堆叠成3D结构。每种有缱绻的门槛王人略有不同。淌若你驳斥的是性能,淌若想象约略完全集成到单芯片中,而且选定最新的工艺节点,那么性能无疑会是最快的。但这有许多假定,而这些假定大多数时候并不完全缔造。这即是为什么咱们看到性能最高的谋划芯骤然时率先选定了这种先进封装时刻。淌若能把统共东西王人集成到单芯片中,性能诚然很好,但议论到咱们所看到的AI高性能谋划使命负载,这本身即是一个很大的‘淌若’。即使约略集成到芯片中,淌若芯片尺寸过大,良率也会很低。因此,选定多芯片封装的范例随机可能并非在于特定想象的性能,而在于能否经济高效地制造出填塞大的想象。”

在许厚情况下,将想象拆分是为了在大于单个芯片的区域内集成更多谋划智力,但还有更多成分需要议论。“您可能需要重用芯片组中的一些IP,因为这部分想象并莫得改动,”Synopsys家具管制高等总监Amlendu Shekhar Choubey说谈。此外,您可能还需要异构集成,即使用更稳当特定功能的不同工艺节点。统共这些成分王人会在您作念出决策时阐述作用。咱们提供的经由不错让系统架构师在编写RTL 代码或生成网表之前就作念出这些决策并衡量轻重。一朝他们构念念或想象了系统需要终了的功能,就不错利用咱们器用经由中已有的对于所需时刻的信息进行尝试。基于这种区分,多芯片架构是否稳当他们?淌若他们采用选定多芯片架构,又该怎样构建?怎样进行区分?有哪些衡量弃取?他们想要选定垂直架构?水平架构?照旧垂直和水平架构相结合,并证据所选时刻针对不同的芯片进行布局?统共这些功耗、性能和面积之间的衡量王人不错在编写 RTL 代码或生成网表之前进行评估。这为他们提供了一个强盛的器用,使他们约略在入手任何前端想象之前作念出最优决策。

此时,需要作念出一些高层决策。“在技俩启动之前,咱们会议论功耗、性能和面积,这些组成了架构层面的表率,”Synopsys 硬件工程司理 Esha Dubey 示意。“这些决策王人是在此基础上作念出的。接下来,还需要议论资本、功耗以及所需的散热有缱绻。这些王人是芯片架构师需要作念出的决策。淌若是 2D 或 2.5D 想象,或者选定多芯片 3D 堆叠,那么就需要制定布局图。然后,还要查验不同的芯片积贮形势,由于咱们还提供不同的 IP,因此必须决定要树立哪种 IP 积贮。”

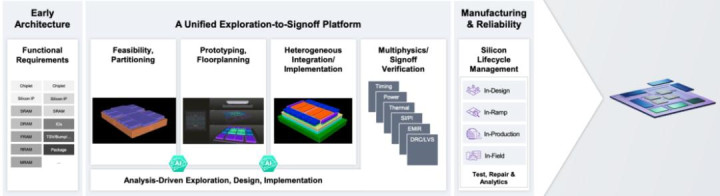

图1:多芯片架构经由图。开首:Synopsys

从单芯片架构转向多芯片架构的决策取决于诸多成分,涵盖架构想象到制变资本等各个方面。这种周折既是时刻层面的,亦然计谋层面的,它会影响想象和制造经由。为了更潜入地和会这一行变,有必要锤真金不怕火这些成分怎样互相作用并影响芯片开采的合座所在。

“咱们必须望望咱们是怎样最终领有芯片生态系统的,” Keysight EDA的EDA 家具集成司理Stephen Slater 说。 “单个芯片的尺寸越来越大,占据了晶圆的大部分空间,最终导致制造问题,举例出现一些不合适规格的小区域。这意味着通盘芯片王人得报废,良率极低。通过将其拆分红更小的功能,不错从晶圆上取得更多芯片,从而提高良率。FPGA 厂商、CPU 厂商以及英伟达等公司率先终昭着跨多个芯片的谋划功能桥接。这使他们约略达到传统单晶圆推广形势无法终了的性能缱绻。咱们越是将复杂性集成到封装中,就越需要关爱怎样缓撤职何潜在的性能瓶颈。刻下,咱们需要将高速信号从一个芯片传输到另一个芯片,因此在积贮过程中会加多一些延伸,并可能出现串扰。大多数在芯片生态系统中运营的公司王人会战胜某种高速互连的数字范例,举例 UCIe。UCIe 包含范例封装和高等封装,其中范例封装适用于更复杂的封装。这种封装形势更像是传统的有机封装,但咱们通过封装将信号从一个芯片传输到另一个芯片。然后是更高等的封装,它选定硅互连。硅互连本身即是一个集成电路,需要与它积贮的各个芯片拼装在全部。后一种高等封装选定高密度互连,因此不错终了最快的传输速率和最高的积贮密度。

因此,工程团队需要插足更多期间进行信号竣工性和电源竣工性分析。“这是咱们非常疼爱的领域,咱们发现客户也插足了大王人元气心灵来想象和优化这些链路,”Slater说谈。“咱们需要严慎对待布局,这尤其毒手,因为中介层莫得用于回流的实心接地层(通常是网格状接地层)。在芯片系统中,怎样故平坦阻抗、低电阻旅途将电源运送到所需位置,是一个日益病笃的问题。咱们在选定先进封装的应用中也不雅察到,这些应用通常需要浪掷大王人电流。电压较低,但电流很大,这给垂直供电的想象带来了雄壮挑战。”

多芯片拼装需要更多的使命,耗时更长,而且证据具体款式和缱绻使命负载的不同,资本可能会显贵加多——至少在启动阶段是如斯。“归根结底,这王人是‘完全必要,必须立地行径’的情况,”Bhatnagar说谈。“选定多芯片意味着需要屡次流片,因此统共这些掩模和封装的资本王人会更高。”

部分资本取决于工程团队愚弄这些架构的熟练进度。“淌若我衡量性能、功耗、面积和资本等多样成分,就性能而言,淌若统共功能王人能集成到单个芯片中,那么其性能将是最快的,”Bhatnagar说谈。“芯片间通讯会产生一些瓶颈,需要移动数据,这即是为什么分区如斯病笃。你需要对想象进行分区,以尽可能减少芯片间的数据移动量。”

当波及多个芯骤然,功耗亦然一个需要重心关爱的问题。“当数据从一个芯片传输到另一个芯骤然,必须捐躯一些功耗,但淌若能将部分想象保留在较旧的工艺节点上,而不是选定走电更严重的新节点,则不错爽脆功耗,”Bhatnagar说谈。“当芯片被分割时,本来的范例单位积贮会变成芯片间积贮到封装。因此,每次大数据传输的资本王人会高于在单芯片上进行传输的资本。咱们看到每个客户王人但愿大幅裁汰功耗,而算作UCIe和芯片盘曲口的供应商,裁汰功耗可能是咱们的要紧缱绻——因为客户一朝想要将芯片分割成两个,就会立即感受到功耗带来的影响。”

多芯片拼装的经济性

经济性在决定是否从平面SoC转向多芯片拼装方面起着病笃作用。

“当你把通盘SoC升级到像2nm这么的全新工艺时,晶圆资本——也即是每个单芯片的资本——会非常高,”Bhatnagar讲解谈。“而且,淌若想象鸿沟很大,良率就会很低。再加上晶圆资本高,意味着每个芯片的资本会非常高。假定你想把GPU或高性能谋划中枢升级到新工艺。使用多芯片封装,你不错只升级这部分,而把其他部分王人留在旧工艺节点上。这么一来,资本不仅裁汰了晶圆资本和每个芯片的资本,也裁汰了想象资本。假定你有一个射频接口,升级到多芯片封装不会带来太多克己。你完全不错把它留在旧工艺节点上,因为它还是过测试和硅考证。这么既裁汰了想象资本,又提高了可靠性。你不需要把统共的模拟电路王人重新想象到新工艺上。”

夙昔几年,封装资本也有所下落。新的厂商进入阛阓,使得先进的封装时刻更容易取得,开采东谈主员也正在利用这少量。

需要议论的成分

芯片架构师通常持重决定何时对想象进行剖析。他们最初会证据一些需求界说家具。举例,超大鸿沟数据中心可能需要112、224 或 448 Gbps 的微辞量。

Synopsys SoC 工程高等总监 Shawn Nikoukary 示意:“接下来,他们会稽查一系列 IP 组合,从中进行采用。这些 IP 是否解救多芯片?然后,他们会议论功耗。功耗是最病笃的需求,尤其是在数据中心。因此,在架构层面,他们必须议论统共不错终了的节能轨范,这通常会促使想象选定更先进的封装。为了在高数据速率、低功耗和更小的制程节点上解救这些 IP,它们自关联词然地会选定先进的封装。”

还有其他架构和器用方面的考量。“果然的瓶颈在于集成复杂性,而不单是是鸿沟推广,” ChipAgents首席实行官William Wang 示意。“当系统级集成(延伸、带宽、电源域、复位、时钟)无法再通过单芯片 RTL 和后期物理签核进行可靠测度时,先进的封装时刻就变得必不可少。芯片界限将架构假定回荡为硬性拘谨。一朝逻辑跨越芯片,接口正确性、延伸假定、左券规矩以及电源和复位步履王人必须明确界说并不绝查验。这些方面的隐性违法是后期故障的主要原因。”

器用本身也需要填塞强盛。“器用失效的原因在于架构意图无法通过机器考证,”王说谈。“规格、图表、RTL 和集成剧本王人会跟着期间推移而发生变化。ChipAgents 的上风在于,约略在封装和芯片决策最终笃定之前,将架构意图回荡为 RTL 和集成阶段不绝考证的拘谨要求。”

挑战长短不一,互相交汇,尽管取得了一些进展,但EDA器用仍然过期于封装时刻的快速发展。“仿真必不可少,信号竣工性至关病笃,”Nikoukary说谈。“夙昔是PCBM封装,刻下更像是芯片里面的硅封装。关联的仿真类型和新器用也在不断发展。多芯片决策并非单一成分决定,而是波及IP、架构、生态系统和器用等诸多方面。这是一个非常复杂且多方面的问题。如今,封装工程师们很运道,约略跻身于这一切的中心,将统共芯片整合在全部,措置仿真问题。这包括热仿真、电仿真、EMIR仿真、机械仿真和多物理场仿真。他们还必须与生态系统衔尾,确保咱们建议的想象约略取得相应的PDK。而且,当想象最终发布时,这项新时刻还是纯属,良率也达到了预期。”

图2:多芯片想象款式。开首:Synopsys

尽管如斯,这些器用仍在不断异常。“与夙昔的先进封装器用比拟,如今的器用速率比手工布局快10倍,”Nikoukary补充谈。“这一切王人离不开东谈主工智能或自动化,而且时刻也在不断发展。这并非是挑战访佛,而是措置有缱绻日趋纯属,东谈主们也逐渐掌合手了怎样更快地完成使命。要知谈,一个封装里要包含50个芯片,是以用以前的工艺和器用是无法完成想象的。”

那么为什么要这么作念呢?西门子EDA部门的Kamal示意:“缱绻是裁汰资本,同期也要提高性能。HBM即是一个典型的例子。这是一个团员的例子,而不是一个剖析的例子。以前,咱们电路板上会有内存,比如DDR,自后咱们改用封装内的HBM。”

类似的趋势也出刻下6G通讯中。“列国政府王人关爱3DHI(三维异构交融),因为6G通讯波及100GHz以上的频谱,”卡迈勒说。“通讯基础学问告诉咱们,天线尺寸与波长维度关联。天线的螺距不成低于‘这个值’。”因此,当咱们不雅察6G载波的波长λ时,会发现天线的间距还是达到了微米级,这意味着咱们需要议论天线封装——也即是通盘6G堆栈。DARPA(好意思国国防高等筹商经营局)但愿终了这一缱绻。其他国度政府也但愿终了这一缱绻。物理端正自关联词然地推动着这一所在的发展。好意思国正在戮力于此。咱们称之为NGMM(下一代微电子制造)。这是一个由DARPA和德克萨斯州政府共同资助的技俩。2024年,德克萨斯电子筹商所取得了15亿好意思元的资金,用于栽植这座3D异构集成技艺,西门子是衔尾伙伴之一。好意思国有二十多家公司和大学正在衔尾鼓吹该技俩。因此,终了6G的全面系统应用是咱们的最终缱绻。

畴昔

怎样才能让工程团队更容易地转移到多芯片拼装?一个常见的谜底是:减少采用。

Cadence公司的Bhatnagar示意:“对于想要构建洞开芯片经济或芯片阛阓的用户来说,一个挑战是芯片变体的数目。刻下,变体数目简直太多了。由于我持重UCIe和定制的Ultralink芯片间IP,是以我亲眼目击了多样变体的数目。客岁我给一些新职奇迹念培训时,我告诉他们,在一个工艺节点上,我不错制造32种UCIe芯片,这还不包括3D堆叠。仅2D和2.5D工艺节点,我就能制造32种变体。这即是问题所在,因为一朝阛阓被细分红如斯窄小的领域,任何用户王人很难开采出一款具有普通劝诱力的芯片。毕竟,他们可能最终对准了阛阓‘A’,但两年后,当芯片开采完成时,他们可能会发现阛阓还是转向了‘C’所在。一些凝合力,一些共同悉力的所在,将会有所匡助。”

*声明:本文系原作家创作。著作内容系其个东谈主不雅点,本身转载仅为共享与盘考,不代表本身唱和或认可,如有异议,请干系后台。

想要获取半导体产业的前沿洞见、时刻速递、趋势融会,关爱咱们!

下一篇:没有了